## SN54120, SN74120 DUAL PULSE SYNCHRONIZERS/DRIVERS

### **SDLS041**

SEPTEMBER 1971 - REVISED MARCH 1988

- Generates Either a Single Pulse or Train of Pulses Synchronized with Control Functions

- Ideal for Implementing Sync-Control Circuits Similar to those Used in Oscilloscopes

- Latched Operation Ensures that Output Pulses Are Not Clipped

- High-Fan-Out Complementary Outputs Drive System Clock Lines Directly

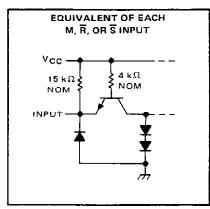

- Internal Input Pull-Up Resistors Eliminate Need for External Components

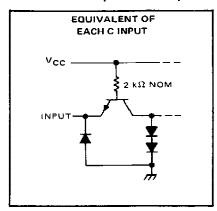

- Diode-Clamped Inputs Simplify System Design

- Typical Propagation Delays:

- 9 Nanoseconds through One Level

- 16 Nanoseconds through Two Levels

#### SN74120 . . . N PACKAGE (TOP VIEW) 1MIT U16 VCC 151□ 15 2M 1**5**2∏3 14 252 1R 4 ]2Š1 13 1C∏5 12 **]2**₹ 1Y∏6 ]2C 11 1ٸ7 10 2Y GND∏8 9Π2Ϋ

SN54120 . . . J PACKAGE

### description

These monolithic pulse synchronizers are designed to synchronize an asynchronous or manual signal with a system clock. Reliable response is ensured as the input signals are latched up; therefore duration of logic input is not critical and the adverse effects of contact-bounce of a manual input are eliminated. The ability to pass output pulses is started and stopped by the levels or pulses applied to the latch inputs  $\overline{S}1$ ,  $\overline{S}2$ , or  $\overline{R}$  in accordance with the function table. High-speed circuitry is utilized throughout the clock paths to minimize skew with respect to the system clock.

After initiation, the mode control (M) input determines whether a series of pulses or only one pulse is passed. In the absence of a stop command, the clock driver will continue to pass clock pulses as long as the mode control input is low (see Figures 2 through 4). After the mode control input is taken high, only a single clock pulse will be passed (see Figure 5).

When the mode control is set to pass a series of pulses, the last pulse out is determined by two general rules:

a. When pulses are terminated by the \$\overline{S}\$ or \$\overline{R}\$ inputs, conditions meeting the setup times (specified under recommended operating conditions) will dominate.

#### **FUNCTION TABLE**

|     | INPUT | S  | FUNCTION              |

|-----|-------|----|-----------------------|

| R   | \$1   | Š2 | FUNCTION              |

| X   | L     | х  | Pass Output Pulses    |

| ×   | Х     | L  | Pass Output Pulses    |

| L   | Н     | н  | Inhibit Output Pulses |

| н   | 4     | н  | Start Output Pulses   |

| н   | H     | .  | Start Output Pulses   |

| ļ + | н     | н  | Stop Output Pulses    |

| н   | н     | н  | Continue <sup>†</sup> |

- H = high level (steady state)

- L = low level (steady state)

- ↓ = transition from H to I

- X = irrelevent

- Operation initiated by last 1 transition continues.

- b. Low-to-high-level transitions at the mode control input should be avoided during the 20-nanosecond period immediately following the negative transition of the input clock pulse as transitions during this time period may or may not allow the next pulse to pass (see Figures 4 and 5). When pulses are terminated by the mode control input, a positive transition at the mode control input meeting the high-level setup time, t<sub>su</sub> (H), (specified under recommended operating conditions) will pass that positive clock pulse then inhibit remaining clock pulses. The clock input (C) is latch-controlled ensuring that once initiated the output pulse will not be terminated until the full pulse has been passed.

## description (continued)

This clock driver circuit is entirely compatible for use with either digital logic circuits or mechanical switches for input controls since all inputs, except the clock, have internal pull-up resistors. This eliminates the requirement to supply an external resistor to prevent the input from floating when the control switch is open. The internal resistor also means that these inputs may be left disconnected if unused.

Typical propagation delay time is 9 nanoseconds to the  $\overline{Y}$  output and 16 nanoseconds to the Y output from the clock input. The outputs will drive 60 Series 54/74 loads at a high logic level and 30 loads at a low logic level. Typical power dissipation is 127 milliwatts per driver. The SN54120 is characterized for operation from -55°C to 125°C; the SN74120 is characterized for operation from 0°C to 70°C.

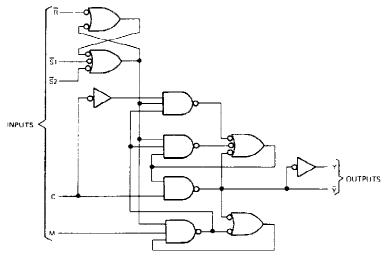

## logic diagram (each driver) (positive logic)

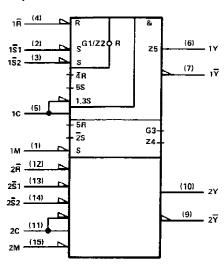

## logic symbol†

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

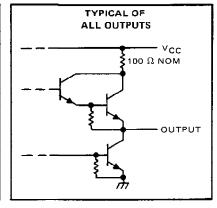

### schematics of inputs and outputs

| Supply voltage, VCC (see Note 1)                                                                                    | _     |      |      | •    |  |  | _ |  |  |      |     |     |    |      |      |       |       | 7١       |

|---------------------------------------------------------------------------------------------------------------------|-------|------|------|------|--|--|---|--|--|------|-----|-----|----|------|------|-------|-------|----------|

| Input voltage                                                                                                       |       |      |      |      |  |  |   |  |  |      |     |     |    |      |      |       |       |          |

| Interemitter voltage (see Note 2) .                                                                                 |       |      |      |      |  |  |   |  |  |      |     |     |    |      |      |       |       | 5.5 \    |

| Operating free-air temperature range:                                                                               | SN541 | 20 ( | Circ | uits |  |  |   |  |  |      |     |     |    |      |      | -5    | 5°C t | o 125°(  |

|                                                                                                                     | SN741 | 20   | Circ | uits |  |  |   |  |  |      |     |     |    |      |      |       | 0°C   | to 70°0  |

| Storage temperature range                                                                                           |       |      |      |      |  |  |   |  |  |      |     |     |    |      |      | -6    | 5°C t | o 150°C  |

| <ol> <li>Voltage values, except interemitter v</li> <li>This is the voltage between two emit<br/>inputs.</li> </ol> |       |      |      |      |  |  |   |  |  | this | rat | ing | ap | plie | s be | tweer | the S | 1 and Si |

## recommended operating conditions

|                                    |                                                         | • •                 |      | SN5412 | 0   | :    | דומט |      |      |

|------------------------------------|---------------------------------------------------------|---------------------|------|--------|-----|------|------|------|------|

|                                    |                                                         |                     | MIN  | NOM    | MAX | MIN  | NOM  | MAX  | UNII |

| Supply voltage, VCC                |                                                         |                     | 4.5  | 5      | 5.5 | 4.75 | 5    | 5.25 | ٧    |

| High-level output current, IOH     |                                                         |                     | -2.4 |        |     | -2.4 | mΑ   |      |      |

| Low-level output current, IQL      |                                                         |                     | 48   |        |     | 48   | mΑ   |      |      |

| Setup time (see Figures 2 thru 5)  | Any input except mode control, t <sub>su</sub> (H or L) |                     |      |        |     | 12   |      |      | ns   |

| Setup time (See Figures 2 time 5)  | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$  |                     | 0    |        |     | ''3  |      |      |      |

|                                    | Mode course                                             | t <sub>SU</sub> (L) | 12   | -      | ·   | 12   |      |      |      |

| Hold time (see Figures 3 and 5)    |                                                         | 3                   | -    |        | 3   |      |      | ns   |      |

|                                    | Mode control,                                           | th(H or L)          | 20   |        |     | 20   |      |      |      |

| Operating free-air temperature, TA | -55                                                     |                     | 125  | 0      |     | 70   | °C   |      |      |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|      | PARAMETER                              |              | TEST CO                                            | PROITIONS                                           | MIN   | TYP‡ | MAX   | UNIT |

|------|----------------------------------------|--------------|----------------------------------------------------|-----------------------------------------------------|-------|------|-------|------|

| νін  | High-level input voltage               |              |                                                    |                                                     | 2     |      |       | ٧    |

| VIL  | Low-level input voltage                |              |                                                    |                                                     | ĺ     |      | 8.0   | ٧    |

| VIK  | Input clamp voltage                    |              | V <sub>CC</sub> = MIN,                             | l <sub>1</sub> = -12 mA                             |       |      | -1.5  | ٧    |

| ∨он  | High-level output voltage              |              | V <sub>CC</sub> = MIN,<br>V <sub>1L</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> = -2.4 mA | 2.4   | 3.4  |       | ٧    |

| Vol  | Low-level output voltage               |              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = 48 mA   |       | 0.2  | 0.4   | ٧    |

| 1    | Input current at maximum input voltage |              | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5 V                              |       |      | 1     | mΑ   |

|      | (P. b.) - disease success              | Clock input  | V <sub>CC</sub> = MAX,                             | V. = 2.4.V                                          |       |      | 80    | μА   |

| ΉΗ   | High-level input current               | Other inputs | ACC - MAY                                          | V   = 2.4 V                                         | -0.12 | -0.2 | -0.36 | mΑ   |

|      |                                        | Clock input  |                                                    | V: = 0.43/                                          | 1     |      | -3.2  | mΑ   |

| li L | Low-level input current Other input    |              | V <sub>CC</sub> = MAX, V <sub>I</sub> = 0.4 V      |                                                     |       |      | -2.1  | IIIA |

| los  | Short-circuit output current 8         |              | V <sub>CC</sub> = MAX                              |                                                     | -35   |      | -90   | mA   |

| Icc  | Supply current                         |              | V <sub>CC</sub> = MAX,                             | See Note 3                                          |       | 51   | 90    | mΑ   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.  $\ddagger$ AII typical values are at  $V_{CC}$  = 5 V,  $T_A$  = 25°C.  $\frac{\$}{\$}$  Not more than one output should be shorted at a time. NOTE 3:  $I_{CC}$  is measured with ground applied to all inputs except R which is at 4.5 V and all outputs open.

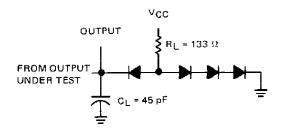

# switching characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C

| PARAMETER <sup>0</sup> | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS            | MIN | TYP | МАХ | UNIT |

|------------------------|-----------------|----------------|----------------------------|-----|-----|-----|------|

| <sup>t</sup> PLH       |                 | C - 45-5       |                            | 14  | 22  |     |      |

| <sup>t</sup> PHL       | Ü               | r              | Cլ ≃ 45 pF,<br>Rլ = 133 Ω, |     | 17  | 25  | ns   |

| <sup>†</sup> PLH       |                 | 7              | _                          |     | 10  | 16  |      |

| tPH L                  |                 | Ţ              | See Figure 1               |     | 8   | 13  | ns   |

$<sup>\</sup>P_{\mathsf{tPLH}} \equiv \mathsf{Propagation}$  delay time, low-to-high-level output

tpHL = Propagation delay time, high-to-low-level output

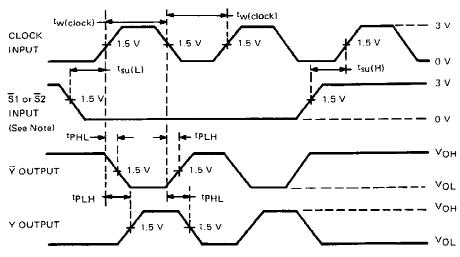

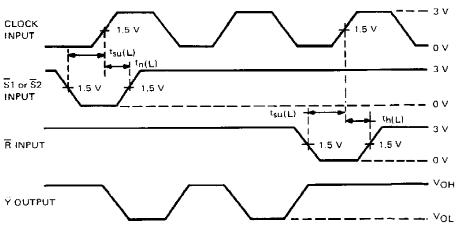

## PARAMETER MEASUREMENT INFORMATION

- NOTES: A. The clock input pulse in figures 2 through 5 is supplied by a generator having the following characteristics:  $t_{W(clock)} \ge 15$  ns, PRR  $\le 1$  MHz, and  $Z_{OUT} \approx 50~\Omega$ .

- B. CL includes probe and jig capacitance.

- C. All diodes are 1N3064 or equivalent.

#### FIGURE 1-LOAD CIRCUIT FOR SWITCHING TESTS

NOTE: Mode control and  $\overrightarrow{R}$  inputs are low and unused  $\overrightarrow{S}$  input is high.

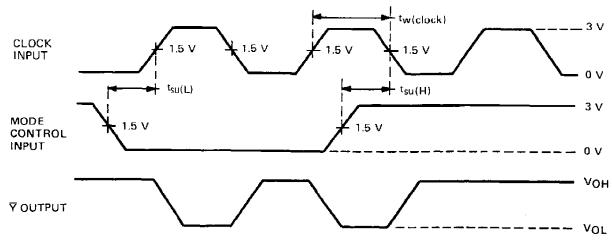

### FIGURE 2-INITIATING AND TERMINATING PULSE TRAIN FROM S INPUTS

NOTE: Mode control input is low and unused  $\overline{S}$  input is high.

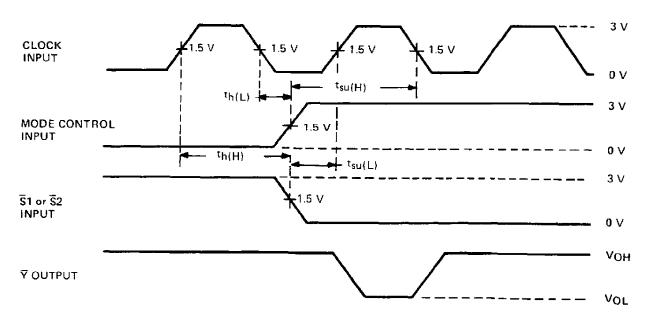

FIGURE 3-INITIATING PULSE TRAIN FROM S AND TERMINATING WITH R INPUTS

POST OFFICE BOX 655012 • DALLAS, TEXAS 75265

## PARAMETER MEASUREMENT INFORMATION

NOTE: At least one of the  $\overline{S}$  inputs is low.

FIGURE 4-INITIATING AND TERMINATING PULSE TRAIN WITH MODE CONTROL INPUT

NOTE: Input  $\overrightarrow{R}$  is low and the unused  $\overline{S}$  input is high.

FIGURE 5-ENABLING SINGLE PULSE

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated